## PRODUCT BRIEF

## IMAGE PROCESSORS

# IP00C331

# 4K60Hz Quad Input 4K Multiple Input/Output De-Interlacer/Scaler LSI

## **Product Description**

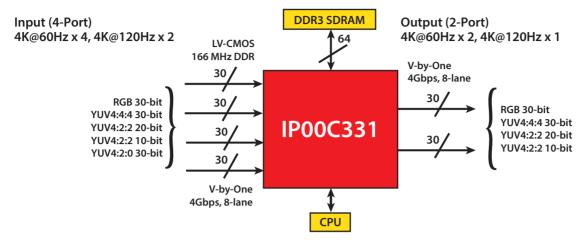

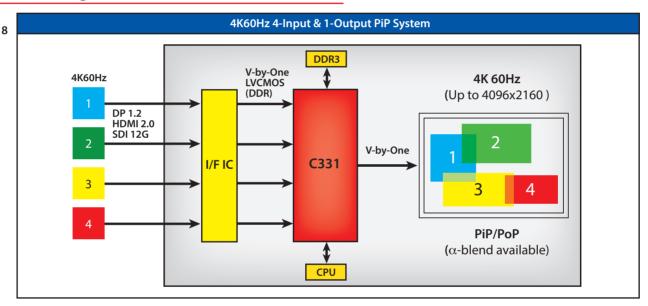

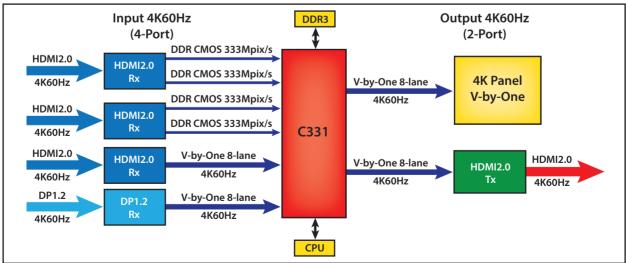

The IP00C331 is a true 4K60Hz up/down scaler with minimal interface requirements. It features 4 input ports up to 4K60Hz each, and 2 output ports up to 4K60Hz each. This allows it to take up to four 4K60Hz sources and scale each one independently to any size and position on a composite 4K60Hz output. Its internal architecture consists of 8 up/down scaler cores plus 4 de-interlacer cores to support interlaced input on each input port. The IP00C331 also features many other high-performance functions such as 90-degree rotation, mirror-flip, PQ and HLG HDR systems (10-bit), and 3DLUT for color management. It makes use of the high-speed serial V-by-One bus interface which is only 8 lanes in order to minimize board footprint. The IP00C331 can be used as a single or dual 4K60Hz scaler, or as a 4K display controller chip supporting multiple inputs.

#### **Features**

#### Input (4K60Hz, 4-port)

- RGB 30bit/YUV4:4:4 30bit/YUV4:2:0 30bit/YUV4:2:2 20bit/YUV4:2:2 10bit(BT656)

@V-by-One 4Gbps, 8-lane 2-port

- <code>@LV-CMOS</code> 166MHz supporting dual (EVEN/ODD) and DDR inputs 4-port

- 4K60Hz input up to 4-port

- 4K120Hz input supported

#### Output (4K60Hz, 2-port)

- RGB 30bit/YUV4:4:4 30bit/YUV4:2:2 20bit/YUV4:2:2 10bit(BT656)

- @V-by-One 4Gbps, 8-lane 2-port

- 4K60Hz dual output (all the time, fully independent)

- 4K120Hz output supported

#### **Input & Output Image Size**

- Horizontal sync signal 16,384 pixels (max) @1ch

- Horizontal image active area 2,176 pixels (max) @1ch

#### **External Memory**

DDR3-SDRAM 64bit PC1600 (4G/2G/1G x16) x4

#### **External/Internal Sync**

- Output sync is compatible only with internal signal

- Independent sync mode is available at each input & output port

## Input/Output Sync/Asynchronous Behavior

- Frame rate conversion

- Tearing protection

- · External force synchronization

- Genlock

#### **De-Interlacer**

- Motion adaptive filter based on Y, U, V, YUV 4:2:2

- All major cadences supported

- Low latency processing (4-port)

#### **Scaler**

- Zoom/shrink 6-symbol programable FIR filter (10bit/pixel)

- Embedded ROM (64set)

#### **Noise Reduction**

- 3DNR (H, V, Temporal)

- MPEG-NR (Mosquito/Block)

- Chroma error filter

#### **Bit Map OSD**

- 256 colors/High color OSD (64K colors)

- Embedded font engine (65536 words)

- Blinking and semi-transparent (4 colors OSD)

- 90-degree rotation, OSD scroll

- Serial flash to bitmap

#### **Image Quality Control**

- Color management (full color gamma)

- 3DLUT (4K60Hz 2-input supported)

- Uniformity correction (by region and per-pixel)

- Bias/Gain/Gamma correction

- H edge enhancement (9symbol) , V edge enhancement (5 to 9symbol)

- Dithering for 10 or 8 bit output

#### **Image Manipulation**

- Mirror/flip/90-degree image

- Vertical keystone

- 4-ch overlay, alpha blending, color key blending

#### **CPU Interface**

8-bit parallel/4-wire serial

## xvYCC/Bt-2020

Fully supported

## **HDR Standard**

SMPTE ST2084(PQ) and HLG both methods supported (RGB 10-bit each)

#### **Power Supply**

3.3V/1.5V/1.1V

#### **Package**

684-pin BGA (0.8mm pitch), 27mmx27mm

## **IP00C331** 4K60Hz Quad Input 4K Multiple Input/Output De-Interlacer/Scaler LSI

## **IP00C331 Block Diagram**

## **Application Diagrams**

"V-by-One" is a trademark of Thine Electronics, Inc.

For more information please visit: www.i-chips.co.jp or info@i-chips.co.jp

## i-Chips Technology, Inc.